東芝、32nm世代以降のLSI向けに導入する高性能化技術を開発〜メタルゲートなど主要課題に目処

エンタープライズ

その他

-

10G光回線導入レポ

-

東芝、「SiLKROAD ONLINE」「Fantasy Odyssey」「大航海時代」の推奨ノートPC——ゲーム内オリジナルアイテムなど付属

-

東芝、新型バッテリー「SCiB」——電気自動車・バイク、産業機器、非常電源などへ応用

今回開発されたのは、32nmに導入する新要素のうち、電流制御用のゲート電極を金属化する「メタルゲート技術」、電流経路内の接触抵抗を抑える「低抵抗コンタクト技術」、「〔110〕面pMOS高性能化技術」、の3種類。

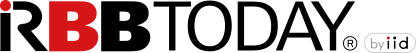

「メタルゲート技術」については、特性の異なるnMOSとpMOSで、従来のような別の金属を用いる複雑な加工方式(デュアルメタル)に替え、金属化合物(シリサイド)を利用。共通材料のニッケルを1:3の割合でpMOS側に多く導入した後、nMOSゲートの界面にアルミ二ウムを偏析させる仕上げ処理のみで、従来と同様の効果を得るプロセスが開発された。この処理では一度の成膜で済むため、プロセスが簡易化されるとのこと。さらに、金属材料をニッケルからプラチナに変えると、nMOS用のアルミニウム効果を保持したまま、pMOS側の仕事関数を4.9eV程度に高められることも検証済みとなっている。

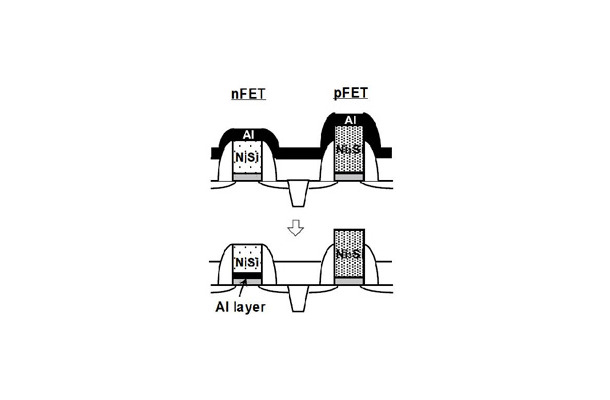

「低抵抗コンタクト技術」については、通電を担うソース・ドレイン電極の金属材料と不純物拡散層のシリコン材料の接触抵抗が大きな性能制約となる課題に対し、nMOS側で接触抵抗の生じる界面に異種金属(希土類金属のイットリウムなど)を導入し、接触抵抗を1/4程度にまで低減させる「メタル偏析プロセス」を開発した。メタルゲート技術と同様に、電極材料をnMOS・pMOS共通とすることが可能で、あわせてプロセスの簡易化が可能となった。

「〔110〕面pMOS高性能化技術」については、特性の詳細な測定を通じて、シリコンの加工方向(基板の面方位)を変えてpMOSを高性能化(高速化)する技術の実用法が開発された。キャリア移動度とともにゲート電極の制御性を決める寄生容量が高くなることが判明し、埋め込みSiGe構造により0.6%程度の局所歪みと組み合わせた32nm世代の試作素子で約19%の高速化を達成したとのこと。また、寄生抵抗などの影響を排した理想条件では、32nm世代は通常の〔110〕面を用いる場合に比べpMOSの移動度が6倍高いことを解明した。

なお、各要素技術については、複数の代替方式を検証した上で、最適に統合する必要があるため、今後全体最適化の観点で比較検証を行うとしている。

これらの新技術については、米国ワシントンD.C.で12月10日から開催されている半導体の国際学会「IEDM」(International Electron Devices Meeting)にて発表が行われている。