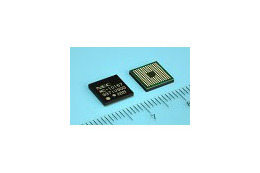

NEC、30nmレベルの高性能・低リークなCMOSを製造するチャネル構造設計技術を開発

エンタープライズ

その他

-

10G光回線導入レポ

-

ACCESS、Linuxベースの携帯用共通プラットフォームを構築へ〜ドコモ、NEC、パナソニック、エスティーモと合意し覚書を締結

-

NEC、台湾・大同電信よりモバイルWiMAX機器一式を受注、初の商用向け受注

今回発表された技術は、不純物のチャネリング抑制を行う「クラスターイオン注入」と活性化アニール時の拡散抑制を行う「高温ミリ秒アニール」を組み合わせ、高活性(低抵抗)かつ微細化に適したチャネル不純物分布を持つ接合を形成できるもの。実デバイスとして試作し、有効性の実証も行われている。また、高分解能の電子線ホログラフィーを応用してトランジスタの断面ポテンシャル分布を測定する独自技術も確立した。これにより、TCAD(Technology CAD)を用いて設計したチャネル構造の精度検証が可能となり、製造プロセスの最適化が可能となった。

微細CMOSの実現においてはリーク電流の増大が問題のひとつとして挙げられているが、リーク電流を抑制するためにトランジスタのチャネル部分に極浅接合を形成する必要がある。今回の技術を利用することで、製造プロセスの変化に応じて大変敏感に変化する接合形状を確認し、プロセスを効率よく最適化できる。今回の技術により、高性能で低リークなプレーナバルクCMOSの30nmレベルまでの微細化が可能であることが実証された。