IC内の配線間を真空にして電気を35%速く流し、消費電力を15%削減できる技術

エンタープライズ

その他

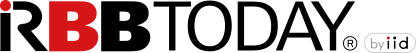

現在のICにおいては、配線間はガラス繊維などの絶縁体で囲んでいるが、配線の精細化が進むにつれて、微量の電気が流れることが問題になる。これが、電気エネルギーの減損や吸収、発熱、データ通信速度の低下につながっている。今回発表された製造技術では、絶縁体に代わり真空を用いて解決している。真空は究極の絶縁体だとしており、同社では「ムーアの法則で2世代分に相当する配線性能の向上を一気にもたらします」としている。

またこの製造技術では、貝殻や雪の結晶片、歯のエナメル質を作り出す自然界のパターン形成プロセスを用いているのが特徴。300ミリのウエハー全体に、20ナノ程度の穴を数兆個も規則的に形成。この穴を真空にすることで、絶縁が作れるようになる。

なお、標準的なCMOSの製造ラインにおいては、製造の中断などを行わずに導入できるとしている。