株式会社図研(本社:神奈川県横浜市、代表取締役社長:勝部迅也)は、2025年12月17日(水)~19日(金)に開催される「SEMICON Japan 2025」に出展します。

図研ブースでは、2.xD/3DIC(三次元集積回路)に対応した最新のアドバンスドパッケージ設計ソリューションや、半導体製造装置開発を支援するソリューションを展示します。

現在、半導体業界は、微細化による性能向上の限界を迎え、チップレットや3DICなどの後工程技術への期待が急速に高まっています。一方、この実現には、半導体の前工程と後工程を密に連携し、チップ・インターポーザー(中間基板)・パッケージを含めたシステム全体を統合的に設計・解析できる環境が不可欠です。

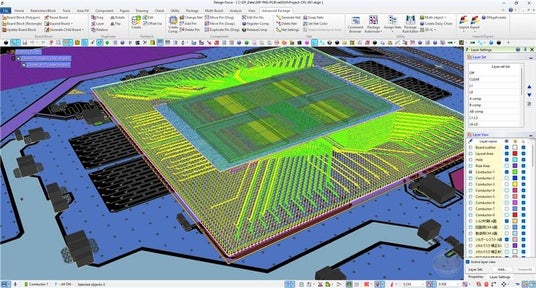

図研は、システムレベル マルチボード設計環境 「CR-8000 Design Force」において、3次元データベースを採用し、SoC/パッケージ/PCBの協調設計など、異なるテクノロジーを持つ複数のオブジェクトを一つのシステムとして統合的に設計・検証できる環境を提供してきました。この環境の強みと実績をいかし、インターポーザーを含む半導体アドバンスドパッケージの設計環境としてパフォーマンスをさらに強化します。そして、テクノロジーパートナーであるSynopsys社の「3DIC Compiler」やAnsys社の解析ソリューションとシームレスに連携することで、従来の分業化による制約や技術的課題を解消し、半導体の前工程・後工程を統合する設計解析環境を実現します。

CR-8000 Design Force 半導体アドバンスドパッケージ統合設計・解析環境

「SEMICON Japan 2025」の図研ブースでは、半導体アドバンスドパッケージ設計を含むシステムレベル設計・検証を支援する「CR-8000 Design Force」や、半導体製造装置開発を支援する図研の電装設計ソリューションの紹介に加え、Synopsys社、Ansys社によるプレゼンテーションも予定しています。

また、当社専務執行役員 CTO 技術本部長 仮屋 和浩は、以下のAPCSおよびADISパネルディスカッションに登壇します。 ぜひ会場にてご覧ください。

APCS2025 パネルディスカッション

未来をつなぐチップレット:光・車・AIが描くサステナブル社会

2025年12月18日(木) 14:30 ~ 16:35 SuperTHEATER(西4ホール内)

ADIS2025 パネルディスカッション

徹底討論『設計のAI活用』と『デジタルツイン』~EDA・半導体ベンダが語る設計現場の最前線

2025年12月18日(木) 9:30~11:00 TechSTAGE SAKURA(会議棟 605-606)

⇒(詳細)SEMICON パネルディスカッションに図研技術本部長 仮屋和浩が登壇

<出展概要>

企業プレスリリース詳細へ

PRTIMESトップへ