東芝、高速生成レートの物理乱数生成回路技術を開発

エンタープライズ

その他

-

10G光回線導入レポ

-

東芝、約11時間バッテリ駆動のweb限定モバイルノートPCなどー—Core 2 Duo U7700搭載

-

東芝、世界最高速833MHzの混載DRAM技術を開発〜画像処理LSIの高速化に期待

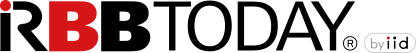

同技術は、乱数源としてトランジスタの窒化シリコン膜が電子を捕捉・放出する際のノイズを利用する同社独自の小型素子を利用し、発生したノイズ信号を乱数に変換するデジタル変換回路に信号を効果的に増幅させる小型のA/Dコンバータを採用することで、回路全体を従来比で9割近く小型化するとともに、乱数の生成レートを実用的レベルである2.0Mbits/sに高速化したもの。生成した乱数は、-50度から100度の範囲で規則性のないことを確認するための標準統計テストを実施し、物理乱数の信頼性課題となる温度依存性がないことも確認されている。

なお、同技術は情報通信研究機構(NICT)による、民間基盤技術研究促進制度を利用した研究課題「高度情報セキュリティに向けた真性乱数生成集積回路の研究開発」の一環として開発されたものだ。

関連ニュース

-

東芝、約11時間バッテリ駆動のweb限定モバイルノートPCなどー—Core 2 Duo U7700搭載

東芝、約11時間バッテリ駆動のweb限定モバイルノートPCなどー—Core 2 Duo U7700搭載

-

東芝、世界最高速833MHzの混載DRAM技術を開発〜画像処理LSIの高速化に期待

東芝、世界最高速833MHzの混載DRAM技術を開発〜画像処理LSIの高速化に期待

-

11gに比べ約3倍の通信速度! Draft11n無線LANルータ/価格9,300円

11gに比べ約3倍の通信速度! Draft11n無線LANルータ/価格9,300円

-

あると便利! 汎用タイプのノートPC用ACアダプタ

あると便利! 汎用タイプのノートPC用ACアダプタ

-

東芝、45nmプロセスCPU搭載のAVノートPC「Qosmio」Webモデル

東芝、45nmプロセスCPU搭載のAVノートPC「Qosmio」Webモデル

-

SBモバイル、「fanfun. 815T 倖田來未 モデル」予約受付開始!〜ド派手なオリジナルポーチも付属

SBモバイル、「fanfun. 815T 倖田來未 モデル」予約受付開始!〜ド派手なオリジナルポーチも付属

-

消費電力を最大75%削減する省エネ外付け型HDD——東芝「REGZA」録画用にも対応

消費電力を最大75%削減する省エネ外付け型HDD——東芝「REGZA」録画用にも対応

-

東芝、X7350×2を標準搭載した4wayラックマウントサーバ

東芝、X7350×2を標準搭載した4wayラックマウントサーバ