インテル、エクサスケールコンピューターに向けた課題を説明

エンタープライズ

ハードウェア

-

10G光回線導入レポ

-

マウスコンピューター、第2世代Coreプロセッサー搭載の省スペースデスクトップPC

-

インテル、6Gbps SATA対応のSSD「SSD 510シリーズ」……250GB/120GB

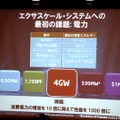

エクサスケールは現在最速のスーパーコンピューターの約1,000倍の処理能力を表し、より高速な処理が必要な医療用画像処理や、ゲノム研究、気候シミュレーションなどで用いられようとしている。エクサスケール実現の課題としてパウロスキー氏は、消費電力の増加をあげる。仮に現在のペタFLOPSの技術の延長でエクサFLOPSを実現した場合、消費電力は4GWにのぼり常識的に供給できる電力量を超えてしまう。パウロスキー氏は、エクサスケール実現に向けては、消費電力の増加を10倍に抑えつつ、性能を1,000倍にまであげる必要があると述べた。

そのためにはパラダイムシフトが必要であるとして、従来の優先事項であるシングル・スレッド性能の向上や、プログラミングの生産性などに代わり、スループット性能の向上や省エネのためのアーキテクチャー機能が重要になるとの見方を示した。

具体的な取り組みとして、パウロスキー氏はDRAMアーキテクチャーの改良をあげる。現在のDRAMにアクセスしてデータを読み取る際、1回に活性化するページが大きく、R/W(リフレッシュ回数)が多い。また読み出したデータの一部しか使用しないため無駄も発生する。改良型のDRAMでは、ページを小さくし、リフレッシュ回数も抑える。また使用するデータのみ読み出すことで効率を上げ、I/Oの広帯域化が可能となる。

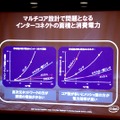

またプロセッサについてパウロスキー氏は、マルチコア化を進めるとインターコネクトの面積と消費電力が問題になるという。コア数が増加するにつれ、リングのインターコネクト面積が増え、クロスバーやリングの消費電力も大きく上がってしまう。

さらにパウロスキー氏は、長距離伝送で電力効率を最大化できるシリコンフォトニクスの研究も進めていくとした。

関連ニュース

-

マウスコンピューター、第2世代Coreプロセッサー搭載の省スペースデスクトップPC

マウスコンピューター、第2世代Coreプロセッサー搭載の省スペースデスクトップPC

-

インテル、6Gbps SATA対応のSSD「SSD 510シリーズ」……250GB/120GB

インテル、6Gbps SATA対応のSSD「SSD 510シリーズ」……250GB/120GB

-

米Intel、McAfeeの買収完了を発表……今年後半には成果発表も

米Intel、McAfeeの買収完了を発表……今年後半には成果発表も

-

インテル、理論値10Gbpsの超高速データ転送技術「Thunderbolt」を発表!

インテル、理論値10Gbpsの超高速データ転送技術「Thunderbolt」を発表!

-

オバマ米大統領がインテルを視察……教育キャンペーンの一環

オバマ米大統領がインテルを視察……教育キャンペーンの一環

-

米Intel、アリゾナ州に半導体工場を50億ドルで建設……14nmのトランジスタ量産へ

米Intel、アリゾナ州に半導体工場を50億ドルで建設……14nmのトランジスタ量産へ

-

インテル×凸版印刷×ビットウェイの電子書籍ストア、「BookLive!」がオープン

インテル×凸版印刷×ビットウェイの電子書籍ストア、「BookLive!」がオープン

-

NEC、IAサーバ「Express5800シリーズ」新モデル8機種を発売……処理性能を従来比最大で20%向上

NEC、IAサーバ「Express5800シリーズ」新モデル8機種を発売……処理性能を従来比最大で20%向上

-

富士通、「PCクラスタ性能検証センター」を強化……本日発表の最新CPU「インテルXeon5600番台」に対応

富士通、「PCクラスタ性能検証センター」を強化……本日発表の最新CPU「インテルXeon5600番台」に対応

-

インテルチップセット不具合を受け、「レッツノート」春モデルが発売延期

インテルチップセット不具合を受け、「レッツノート」春モデルが発売延期