日立、サーバ装置内の通信性能を向上させる送受信回路技術を開発〜低雑音設計により従来比20%の省電力化

ブロードバンド

その他

-

10G光回線導入レポ

-

日立、コンテンツアーカイブ専用ストレージを拡充〜メールアーカイバ「WISE Audit」と連携

-

スワロフスキーの大粒クリスタルで装飾したカナル型イヤホン——10色カラバリ&抗菌加工も

大容量化、高速化が要求されるデータ通信において、ボトルネックとなっているサーバ装置内の通信性能を向上させると同時に、サーバやストレージ、通信機器などに適用することで、大幅な省電力化を実現するのが狙い。

サーバ装置内のデータ通信は、装置の筐体内にあるバックプレーンと呼ばれるスロット、コネクタが付けられたプリント回路基板を介して行われるが、信号が伝送される距離(通常20〜80cm)が長くなるほど、バックプレーン上を流れるデータ信号波形の歪みが大きくなり、正しい信号が送れなくなる。この問題を解決するため、さまざまな方法が考え出されているが、今回、日立は、クロック生成回路と受信クロック抽出回路の最適化設計により、クロック信号のタイミングの変動を抑制することでDFEなどの複雑な信号処理技術を使わずに、8Gb/sまで通信速度を向上させた。また、160mW/レーンの省電力設計により、テストチップ上にデータ送受信回路を21レーン搭載することに成功した。

日立はすでに、通信速度5Gb/sのデータ送受信回路を情報・通信装置用LSIに採用・製品化しているが、今回の技術は、消費電力を20%低減できるという。今後、次世代のターゲットである8Gb/s通信において、大容量化や高速化に伴う消費電力増大などの課題を解決し、1〜2年後の実用化をめざすとのこと。

なお、本開発の技術的詳細は、18日から米国・ホノルル市で開催された半導体集積回路に関する国際会議「2008 Symposium on VLSI Circuits」にて発表されている。

関連ニュース

-

日立、コンテンツアーカイブ専用ストレージを拡充〜メールアーカイバ「WISE Audit」と連携

日立、コンテンツアーカイブ専用ストレージを拡充〜メールアーカイバ「WISE Audit」と連携

-

スワロフスキーの大粒クリスタルで装飾したカナル型イヤホン——10色カラバリ&抗菌加工も

スワロフスキーの大粒クリスタルで装飾したカナル型イヤホン——10色カラバリ&抗菌加工も

-

日立と東大生産技研、将来のスパコンにつながる大幅なLSI省電力技術を開発

日立と東大生産技研、将来のスパコンにつながる大幅なLSI省電力技術を開発

-

日立、USBメモリを利用した電子割符方式セキュリティソフト「割符ランチャーセット」

日立、USBメモリを利用した電子割符方式セキュリティソフト「割符ランチャーセット」

-

SBモバイル他7社、PayPass+NFCケータイを使った非接触決済の実証実験を浦安で開始

SBモバイル他7社、PayPass+NFCケータイを使った非接触決済の実証実験を浦安で開始

-

「就職」と「転職」の違いは人気企業の違い——DODA転職人気企業ランキング2008

「就職」と「転職」の違いは人気企業の違い——DODA転職人気企業ランキング2008

-

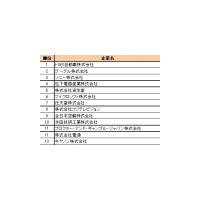

IIJグループら10社、日本セキュリティオペレーション事業者協議会を設立

IIJグループら10社、日本セキュリティオペレーション事業者協議会を設立

-

映像メーカー業界団体「DEG(デジタル・エンターテイメント・グループ)ジャパン」設立

映像メーカー業界団体「DEG(デジタル・エンターテイメント・グループ)ジャパン」設立

-

日立、既存電話環境に対応したアプリケーション/電話システム連携ソフトウェア

日立、既存電話環境に対応したアプリケーション/電話システム連携ソフトウェア

-

日立、ネットTV向けHTTPストリーミングサーバシステムとコンテンツ制作支援システム

日立、ネットTV向けHTTPストリーミングサーバシステムとコンテンツ制作支援システム