産総研、SRAMの新回路構成を考案〜従来比1.5倍の動作安定、22nm世代メモリの問題解決にメド

エンタープライズ

その他

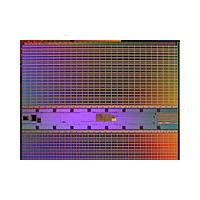

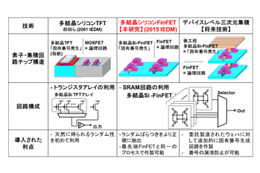

素子微細化の難度は年々高くなってきており、2013年以降に市場投入が想定されている22nm世代トランジスタ技術では、素子寸法が現在の半分に縮小されるのに伴い、素子性能のばらつきが重大な問題になると危惧されていた。特にSRAMでは、チップ上で最小寸法のトランジスタを多用するために、この問題の影響を受けやすい。

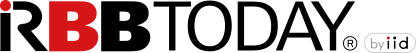

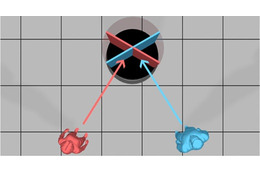

今回考案されたSRAM回路は、「フィン型マルチゲート電界効果型トランジスタ」(フィン型FET)と呼ばれる立体型新構造トランジスタと、これに電流駆動力を調整する機能を加えた4端子フィン型FETによって構成される。4端子フィン型FETを書き込み・読み出し回路と記憶保持部を接続する部位に用い、この部位の電流駆動力を書き込み・読み出しの動作に応じて動的に切り替えることによって、それぞれの動作安定性を向上させることができる。

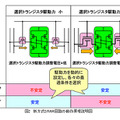

新方式では、選択トランジスタを電流駆動力可変の4端子フィン型FETにしたことにより、書き込み時には電流駆動力を大きくしてビット線-フリップフロップ回路間の結合を高め、逆に読出し時には電流駆動力を小さくし結合力を低めることが可能。シミュレーションによる検討の結果、従来の平面型トランジスタでSRAM回路を実現する場合に比べて、1.5倍の動作安定性が書き込み・読み出しの両動作で実現されるとの見通しを得た。22nm世代トランジスタ技術において、従来と同じ構成のSRAMを用いると歩留まりの問題が生じるが、本SRAM回路を用いれば解決できることになる。今回得られた計算結果の単純な換算を行うと、2013年に市場投入想定の量産型システムLSIに搭載されるSRAMでも十分な歩留まりが得られることになる。

今後は、今年度から実施の、経済産業省の研究開発プロジェクト「ナノエレクトロニクス半導体新材料・新構造技術開発−うち新材料・新構造ナノ電子デバイス」を通じて、原理実証を行う予定だ。

なお、この成果は、9月17〜19日に米国サンノゼ(シリコンバレー)で開催される国際会議「カスタム集積回路会議」(2007 Custom Integrated Circuits Conference)にて注目論文として発表される。