日立と東大生産技研、将来のスパコンにつながる大幅なLSI省電力技術を開発

ブロードバンド

その他

-

10G光回線導入レポ

-

【地域WiMAX:機器ベンダーに聞く】専業メーカーの強みとOpen WiMAX戦略とは——アルバリオン

-

日立、USBメモリを利用した電子割符方式セキュリティソフト「割符ランチャーセット」

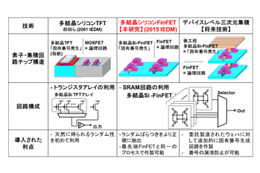

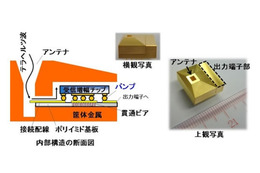

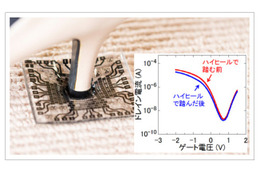

スーパーコンピュータは、多数のプロセッサが並列に動作することにより大規模な計算を行うが、高性能化が進むと、近い将来、消費電力が10メガワット級になると予測されている。一般的にLSIの消費電力増大をもたらす主要因は、「動作電力」と、動作していないとき(待機状態)に流れる「リーク電流」の2つに分かれるが、携帯電話など小型情報機器では動作パターンの解析が進み、基板電圧を制御することで待機状態のLSIのリーク電流を削減する方式が開発されてきた。スーパーコンピュータでも、プログラムによっては計算処理を行っていないプロセッサが存在することから、それらのプロセッサの周波数と基板電圧をきめ細かく制御して、動作電力とリーク電流を削減可能との予測から、日立と東大桜井教授の研究グループが開発に取り組んでいた。

その結果、スーパーコンピュータで大規模計算を行う際に、プログラムのパターンによって計算処理を行うプロセッサを特定できることを利用し、プロセッサの動作周波数と基板電圧を調整できる回路(レジスタ回路)を設けて、計算処理を行わないプロセッサの周波数を下げるとともに、基板電圧を調整することによって、リーク電流を削減することに成功した。これにより、LSIの省電力化を図るとともに、スーパーコンピュータ全体での省電力化が可能となったとのこと。90nmプロセスの4個のプロセッサを搭載した実験用LSIを試作して実証実験を行ったところ、LSIの消費電力を最大で約50%削減できる見通しが得られたという。

なお、本研究は、文部科学省科学技術試験研究委託事業による委託業務「低電力高速デバイス・回路技術・論理方式の研究開発」にて、実施された。また本成果は18日から米国・ホノルル市で開催されている半導体集積回路に関する国際会議「2008 Symposium on VLSI Circuits」にて発表された。

関連ニュース

-

【地域WiMAX:機器ベンダーに聞く】専業メーカーの強みとOpen WiMAX戦略とは——アルバリオン

【地域WiMAX:機器ベンダーに聞く】専業メーカーの強みとOpen WiMAX戦略とは——アルバリオン

-

日立、USBメモリを利用した電子割符方式セキュリティソフト「割符ランチャーセット」

日立、USBメモリを利用した電子割符方式セキュリティソフト「割符ランチャーセット」

-

マクセル、大口径直径13mmドライバユニット搭載のカナル型イヤホン

マクセル、大口径直径13mmドライバユニット搭載のカナル型イヤホン

-

SBモバイル他7社、PayPass+NFCケータイを使った非接触決済の実証実験を浦安で開始

SBモバイル他7社、PayPass+NFCケータイを使った非接触決済の実証実験を浦安で開始

-

IIJグループら10社、日本セキュリティオペレーション事業者協議会を設立

IIJグループら10社、日本セキュリティオペレーション事業者協議会を設立

-

映像メーカー業界団体「DEG(デジタル・エンターテイメント・グループ)ジャパン」設立

映像メーカー業界団体「DEG(デジタル・エンターテイメント・グループ)ジャパン」設立

-

日立、既存電話環境に対応したアプリケーション/電話システム連携ソフトウェア

日立、既存電話環境に対応したアプリケーション/電話システム連携ソフトウェア

-

日立、ネットTV向けHTTPストリーミングサーバシステムとコンテンツ制作支援システム

日立、ネットTV向けHTTPストリーミングサーバシステムとコンテンツ制作支援システム

-

ポート増設に便利、ループ防止・認証機能搭載ローコストスイッチ——日立電線

ポート増設に便利、ループ防止・認証機能搭載ローコストスイッチ——日立電線

-

日立、集約度をさらに高めるサーバ仮想化機構「Virtage Version 3」発表〜仮想化オーバヘッドを最大25%低減

日立、集約度をさらに高めるサーバ仮想化機構「Virtage Version 3」発表〜仮想化オーバヘッドを最大25%低減