書き換え回数1億回以上、書き込み電圧6V以下を実証——産総研、強誘電体NANDフラッシュメモリー

エンタープライズ

その他

発表によると、従来型のNANDフラッシュメモリーのメモリーセルの書き換え回数が1万回、書き込み電圧が20Vなのに対し、今回作製したメモリーセルの書き換え回数は1億回以上、書き込み電圧は6V以下となる。また、従来のNANDフラッシュメモリーの微細化の限界は30nm程度といわれているが、今回作製したメモリーセルの技術を強誘電体NANDフラッシュメモリーに応用することにより、将来の20nm、10nm技術世代にも対応できるため、次世代高密度大容量不揮発メモリーとして期待できる。

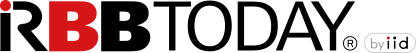

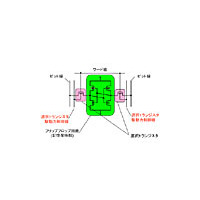

同研究では、NANDフラッシュメモリーセルとして最適なしきい値をもつようにチャネル領域への不純物注入条件を調整したp型Si半導体基板上にパルスレーザー蒸着法によって高誘電体Hf-Al-O薄膜を約10nm、強誘電体SrBi2Ta2O9薄膜を約400nm製膜した後、金属Ptを約200nm製膜し、フォトリソグラフィー技術によりゲートおよびソース、ドレイン、基板の各電極を形成して金属-強誘電体-絶縁体-半導体(MFIS)ゲート積層構造をもつnチャネル型FeFETが作製された。FeFETにパルス幅の異なる書き込み・消去電圧を与えてからしきい値を測定したところ、10μs、6Vの高速・低電圧パルスによっても2つの記憶状態に相当するしきい値が十分に判別できたほか、メモリーセルにデータ書き込みやデータ読み出しを行う際に同時に隣接するメモリーセルに加わる電圧負荷条件(書き込みディスターブ、あるいは読み出しディスターブ)を、FeFETに加えてしきい値の変化を調べ、メモリーセルへの書き込みや読み出しによって、隣接するメモリーセルの記憶データが誤って書き換えられることのない電圧条件が得られた。

このnチャネル型FeFETは外挿値で10年間のデータ保持が期待され、10μs、6Vの書き込み・消去電圧パルスを各々1億回まで印加してnチャネル型FeFETのしきい値の変化を調べたところ、1億回のパルス印加後でも大きなしきい値の変化は見られず1億回以上の書き換え耐性をもつことが示された。

同研究所では、今後はFeFETの微細化・集積化技術の開発を進めながら東京大学と共同でFe-NANDフラッシュメモリーアレイの回路設計と作製を行い、Fe-NANDフラッシュメモリーアレイの動作を実証するとしている。

関連ニュース

-

産総研、赤外線を使ってアスベストを溶融・無害化する技術を開発

産総研、赤外線を使ってアスベストを溶融・無害化する技術を開発

-

JSTと産総研、屋内でも使用可能な携帯電話向け自律型測位システム

JSTと産総研、屋内でも使用可能な携帯電話向け自律型測位システム

-

産総研、夢の次世代不揮発性メモリ「スピンRAM」の駆動力の直接測定に成功〜最適設計の評価技術を確立へ

産総研、夢の次世代不揮発性メモリ「スピンRAM」の駆動力の直接測定に成功〜最適設計の評価技術を確立へ

-

産総研、複数の高精細入力映像を自由にレイアウトして表示できる装置を開発

産総研、複数の高精細入力映像を自由にレイアウトして表示できる装置を開発

-

産総研、SRAMの新回路構成を考案〜従来比1.5倍の動作安定、22nm世代メモリの問題解決にメド

産総研、SRAMの新回路構成を考案〜従来比1.5倍の動作安定、22nm世代メモリの問題解決にメド

-

産総研、光で光を制御する新原理の超高速光半導体スイッチを開発〜ネットの超高速化に期待

産総研、光で光を制御する新原理の超高速光半導体スイッチを開発〜ネットの超高速化に期待

-

空間に描画!——バートン、産総研、浜松ホトニクスの3Dディスプレイ技術の性能アップ

空間に描画!——バートン、産総研、浜松ホトニクスの3Dディスプレイ技術の性能アップ

-

ヤフー、産総研と共同でフィッシング詐欺防止技術を開発

ヤフー、産総研と共同でフィッシング詐欺防止技術を開発

-

Hoster-JP、産総研が進める仮想データセンタ実験にホスティングサービスを提供

Hoster-JP、産総研が進める仮想データセンタ実験にホスティングサービスを提供